Intel Broadwell-EP处理器评测

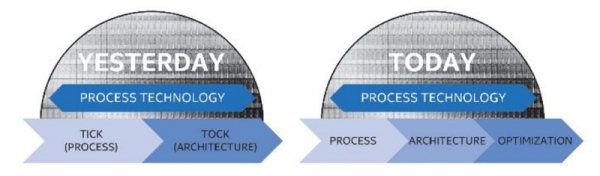

【ZD Research】在以往,Tick-Tock钟摆策略让Intel(英特尔)的处理器每两年更换一次工艺制程(Tick)、每两年更新一次微架构(Tock),最终就是每年换一次制程或微架构,从而每年都能有新产品推出。现在,这个摆动的变慢我们已经用肉眼就可以看到,大致上,在微架构更换之后,还可能会接着推出一个同制程同微架构的改进版本,这样微架构周期就变成了约三年,例子就是桌面端的Broadwell-Skylake-Kaby Lake以及下一个循环中的Cannonlake-Ice Lake-Tiger Lake。

从Tick-Tock变为Process-Architecture-Optimization,笔者将其称为“Tick-Tock-Tock”(非官方)

新的策略称为“Process-Architecture-Optimization”——“制程-架构-优化”,导致这个变长的周期的原因就是临近10nm之后,新工艺制程的开发难度加大。上一代的企业级处理器产品线——代号Haswell-EP的企业级第三代至强E5处理器(Xeon E5 v3)在2014年9月发布,到现在代号Broadwell-EP的企业级第四代至强E5处理器(Xeon E5 v4),中间的跨度超过了一年半。相比消费级,企业级处理器具有很多额外的特性,从而需要额外的开发时间,导致了其周期变长,这种与消费级处理器的不匹配以后还可能会导致一些问题。

2016年4月,Intel Xeon E5-2600 v4处理器,代号Broadwell-EP(14nm,Broadwell微架构)

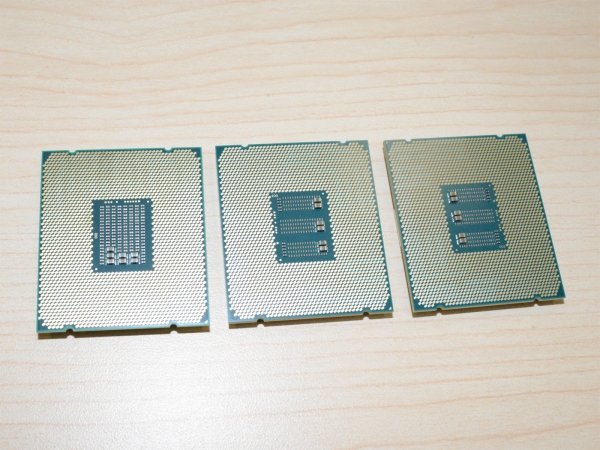

上图是我们拿到的Broadwell-EP——Xeon E5-2600 v4的实物。大约在发布前一个月,我们拿到了样品。在收到处理器(以及搭配的DDR4内存)的同时,笔者身处Oregon的Hillsboro,同时见到了Xeon E5 v4处理器、Xeon E7 v4处理器以及Xeon E5 v4的晶圆,其时Intel对晶圆的官方图片三缄其口,事实证明之后的发布会Intel再也没有提供详细的晶圆照片。幸运的是,在某Workshop上,笔者拍摄了一些晶圆照片,它们经过了Intel人员的审核,在后面我们会看到。

一颗Intel Xeon E5 v4和两颗Intel Xeon E7 v4(正面)

一颗Intel Xeon E5 v4和两颗Intel Xeon E7 v4(背面)

Process-Architecture-Optimization策略中包含了Broadwell,按照设计,Broadwell-EP和所有的Broadwell一样,都基于新的14nm工艺。这个新工艺带来了更多的晶体管,从而达到了更多的核心数量。除此之外,一如既往地,Broadwell-EP在Uncore区域做了很多的改变,有一些非常激动人心,就如我们接下来会看到的一样。

Intel Broadwell-EP处理器评测 by ZD Research 盘骏/Lucifer

首先,我们会先对Broadwell-EP的架构进行一个概述,然后是对Broadwell-EP的微架构改进进行解析,然后着重对Broadwell-EP的Uncore区域——内联架构——当中的上面提到的激动人心的改进进行介绍,然后是一些杂项Uncore改进,最后是平台方面的变化,然后就是性能测试并与前几代理器进行性能对比。

前两代处理器Ivy Bridge-EP和Haswell-EP的评测:

好文章,需要你的鼓励

谷歌Project Genie新增街景功能,带你探索真实世界

谷歌宣布为旗下互动世界构建工具Project Genie新增Google街景功能,用户可基于真实地点生成可探索的游戏世界。只需选定美国境内的地图位置,描述角色形象,并选择"沙漠"或"石器时代"等风格,系统即可生成与现实街景绑定的沉浸式虚拟场景。每次游玩时长限60秒,支持WASD操控,目前仅向AI Ultra订阅用户开放,后续将逐步扩展覆盖范围。

新加坡国立大学发布首个视频“潜台词“理解基准测试:AI究竟能不能读懂视频背后的弦外之音?

新加坡国立大学构建了首个视频隐喻理解基准ViMU,含588段视频与2352道题,测试16个主流AI模型均未超过50%,揭示AI在视频潜台词理解上的系统性短板。

手机上的“氛围编程“时代正式来临

随着AI编程工具的普及,越来越多的非开发者开始尝试自己构建应用。谷歌在I/O大会上宣布,AI Studio新增功能可让用户通过提示词快速生成原生Android应用,并直接导出到手机。此外,谷歌还推出了基于Gemini的自定义小组件功能,并提出"生成式UI"概念,让手机界面根据需求实时生成。与此同时,苹果据报道也在探索通过提示词创建快捷指令的功能,手机个性化体验或将迎来新突破。

浙江大学联合多所顶校:让AI真正“看懂“360度全景图,机器人导航和视觉搜索迎来新突破

浙江大学等机构联合提出PanoWorld,通过球面空间交叉注意力和57万张全景图训练数据,让AI能直接理解360度全景图的空间结构,在导航和视觉搜索任务中大幅超越现有方法。